实验现象:

通过FPGA 的一个I/O 口连接LED;设定I/O 为输出模式。内部乘法器完成乘法计算后

改变输出LED 的状态(红色LED 闪烁)。

核心代码:

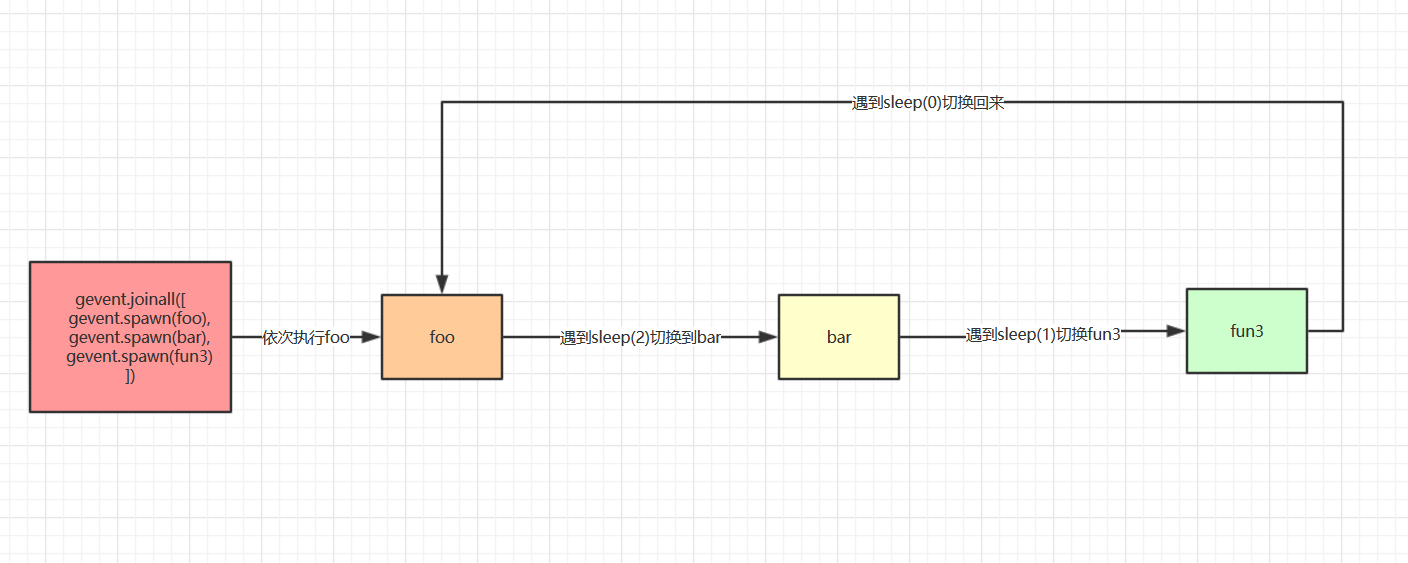

module MULT(input CLK_12M,output FPGA_LEDR ); //------------------rst_n-------------------------// reg [3:0]cnt_rst;reg rst_n;always@(posedge CLK_12M) //产生复位信号beginif(cnt_rst==4'd15)begincnt_rst = 4'd15;rst_n =1'd1;endelse cnt_rst <= cnt_rst + 1'd1;end//--------------------CLK_10Hz--------------------// reg [20:0]cnt;reg CLK_10HZ;always@(posedge CLK_12M)beginif(!rst_n)beginCLK_10HZ <= 1'd0;cnt <= 21'd0;end else if(cnt==21'd1199_999)begin CLK_10HZ <=~CLK_10HZ;cnt <= 21'd0;endelse cnt <= cnt + 1'd1;end//----------------data_in&data_out---------------// reg [7:0]a;always@(posedge CLK_10HZ)beginif(!rst_n)a<= 8'd0;else if(a==8'd255)a <= 8'd0;else a <= a + 1'd1;end//------------------my_mult--------------------// wire [15:0]out;my_mult u1(.dataa(a),.datab(a),.result(out));assign FPGA_LEDR = out[6];//-------------==---endmodule------------------// endmodule

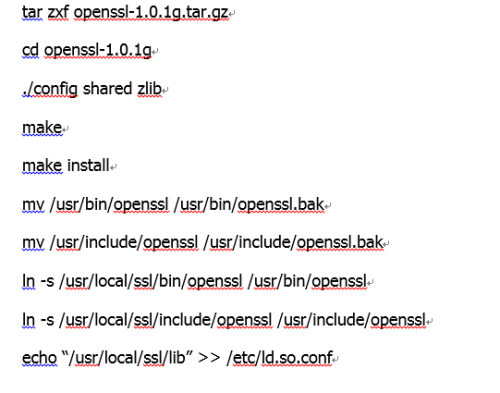

实验方法及指导书:

链接:http://pan.baidu.com/s/1o8KCaTW 密码:n3fg